Beim Entwickeln von Schaltungen hat man es immer mit toleranzbehafteten Bauteilen zu tun, welche die Funktionalität der Schaltung mehr oder minder stark beeinflussen können. Um den Einfluss von Bauteiltoleranzen auf die uns interessierenden Ausgangsgrößen zu ermitteln, bietet sich eine Simulation mit LTSpice an. Verbreitete Methoden wie die Monte-Carlo-Analyse sind bereits in LTSpice integriert. Dieser Beitrag beschäftigt sich mit einem vereinfachten, deutlich schnellerem Analyseverfahren, der Worst-Case Analyse, welche nur die äußersten Grenzwerte der Bauteiltoleranzen berücksichtigt.

Worst-Case bei einer einfachen Stromquelle

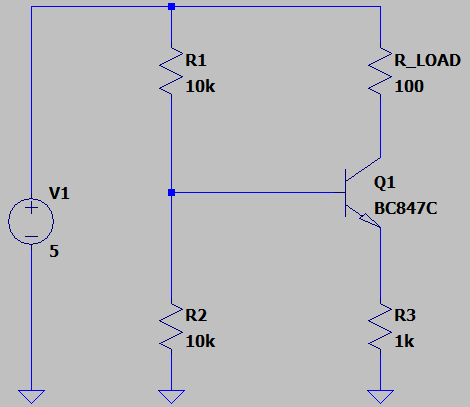

In diesem Beispiel sehen Sie den Aufbau einer einfachen Stromquelle mit einem npn-Transistor, 3 Widerständen (R1, R2 und R3) sowie einem Lastwiderstand (R_LOAD). Der Strom durch den Lastwiderstand ist dabei „lastunabhängig“ auf circa 1,84 mA eingestellt.

Um den Einfluss der Widerstandstoleranzen von R1, R2 und R3 auf den Laststrom durch R_LOAD zu bestimmen, bietet LTSpice mehrere vorgefertige Funktionen, um Bauteilwerte über mehrere Simulationsläufe zu variieren.

- gauss(x), eine Zufallszahl mit Gaußverteilung mit einem Sigma von x

- flat(x), eine Zufallszahl zwischen x und -x mit Normalverteilung

- mc(x,y), eine gleichverteilte Zufallszahl zwischen x*(1+y) und x*(1-y)

All jene Funktionen bieten dann einen Vorteil, wenn es um die Verteilung der Streuung geht. Will ich als Entwickler jedoch nur abschätzen können, was im schlimmsten Fall aus meiner Schaltung herauskommt, dann sind diese Analyseverfahren oft sehr zeitaufwendig, da sehr viele Simulationsdurchläufe absolviert werden müssen, um mit hoher Wahrscheinlichkeit auch die Randwerte meiner Bauteiltoleranzen zu erwischen. Hier bietet sich ein anderes Verfahren an, welches mit Hilfe zweier manuell hinzugefügter Funktionen einfach realisierbar ist.

Worst-Case Analyse Funktionen

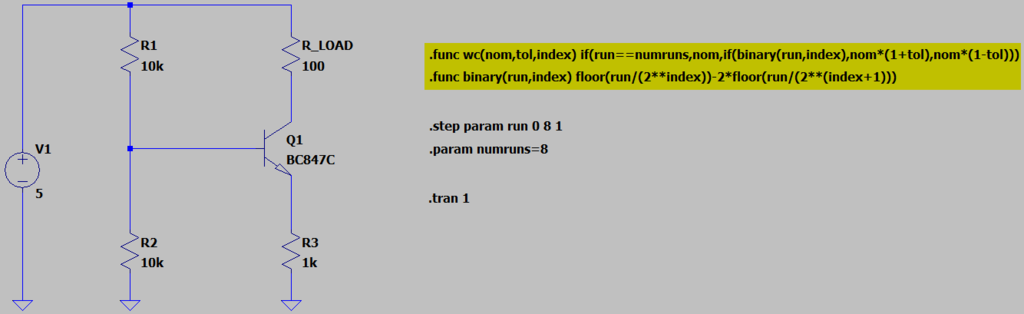

Dieses sogenannte Worst-Case-Analyseverfahren wird implementiert, indem man zwei Funktionen als Spice Directive in den zu analysierenden Schaltplan einfügt. Diese Funktionen sind:

.func wc(nom,tol,index) if(run==numruns,nom,if(binary(run,index),nom*(1+tol),nom*(1-tol)))

.func binary(run,index) floor(run/(2**index))-2*floor(run/(2**(index+1)))

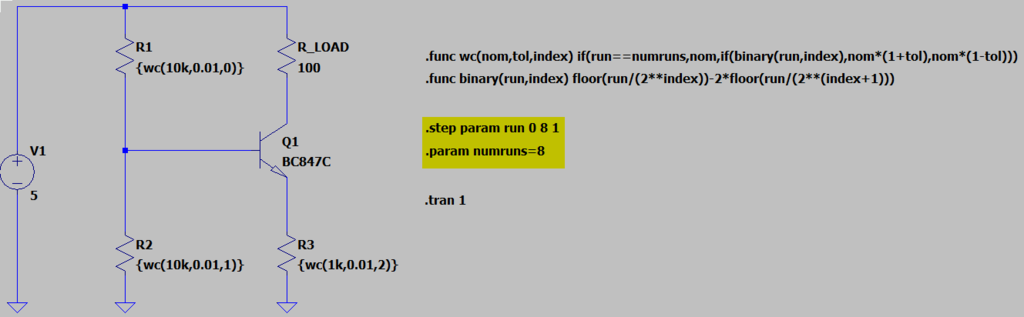

Sind beide Funktionen auf den Schaltplan kopiert, können die Bauteilwerte von R1, R2 und R3 verändert werden. Dazu fügen wir für den jeweiligen Bauteilwert die Funktion {wc(nom,tol,index)} mit entsprechenden Werten ein. Für die Widerstandstoleranz wurde in unserem Beispiel ein Wert von 1% gewählt.

Für R1: {wc(10k,0.01,0)}

Für R2: {wc(10k,0.01,1)}

Für R3: {wc(1k,0.01,2)}

Beachten Sie dabei, dass jedem Bauteil neben dem Nominalwiderstandswert und der Toleranz auch ein fortlaufender Index, beginnend bei 0, zugewiesen werden muss. Um die Simulation starten zu können, fehlen noch die Informationen über die Anzahl der zu vollführenden Durchläufe. Bei 3 zu variierenden Bauteilen ergibt sich eine Durchlaufzahl von 2^n+1. In unserem Fall also 9 Durchläufe. Dies teilen wir LTSpice mit, indem wir die beiden folgenden Spice-Directives auf den Schaltplan legen:

.step param run 0 8 1

.param numruns=8

Simulationsergebnis

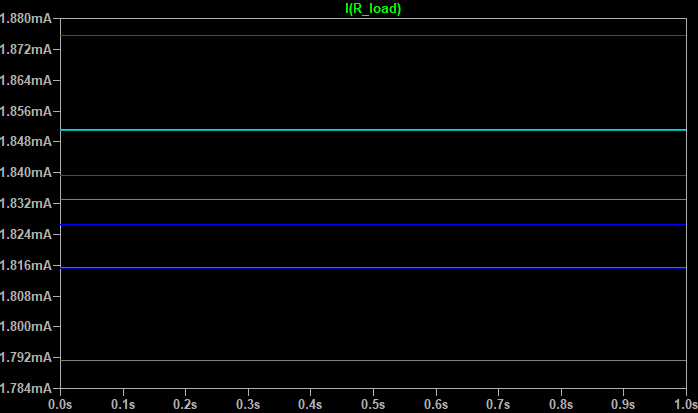

Anschließend können wir die Simulation starten und sehen folgendes Ergebnis:

Je nachdem, welche Bauteile geliefert wurden, kann es also sein, dass der Strom zwischen 1,79 mA und 1,88 mA variiert, was bei einem Nominalstromwert von 1,84 mA bereits mehr als 2% Abweichung sind. Dies kann nun vom Entwickler entsprechend interpretiert und damit eine Beurteilung zur Tauglichkeit der Schaltung vorgenommen werden. Am Rande erwähnt sei noch, dass in einer realistischeren Beurteilung auch die Toleranz der Spannungsversorgung und des npn-Transistors durchgeführt werden müsste, was ebenfalls mit der Worst-Case-Funktion realisierbar ist.

Bei Fragen zu diesem Analyse-Verfahren oder allgemein zu Simulationen in LTSpice, zögern Sie nicht und melden sie sich bei uns. Wir helfen Ihnen gerne weiter.